# ISP Manual 1994

# Lattice In-System Programmability Manual 1994

Copyright © 1994 Lattice Semiconductor Corporation

E²CMOS, GAL, ispGAL, ispLSI, pDS, pLSI, Silicon Forest and UltraMOS are registered trademarks of Lattice Semiconductor Corporation. Generic Array Logic, ISP, ispCODE, ispDOWNLOAD, ispGDS, ispSTREAM, Latch-Lock, Lattice, pDS+ and RFT are trademarks of Lattice Semiconductor Corporation

All brand names or product names mentioned are trademarks or registered trademarks of their respective holders.

Lattice Semiconductor Corporation products are made under one or more of the following U.S. and international patents: 4,761,768 US, 4,766,569 US, 4,833,646 US, 4,852,044 US, 4,855,954 US, 4,879,688 US, 4,887,239 US, 4,896,296 US, 5,130,574 US, 5,138,198 US, 5,162,679 US, 5,191,243 US, 5,204,556 US, 5,231,315 US, 5,231,316 US, 5,237,218 US, 5,245,226 US, 5,251,169 US, 0194091 EP, 0196771B1 EP, 0196771 UK, 0196771 WG.

LATTICE SEMICONDUCTOR CORP. 5555 Northeast Moore Court Hillsboro, Oregon 97124 U.S.A.

Tel.: (503) 681-0118 FAX: (503) 681-3037

#### **About This Manual**

#### **Background**

Lattice Semiconductor Corporation, founded in 1983 and based in Hillsboro, Oregon, has been providing innovative solutions to the manufacturers of high-performance systems for over a decade. Lattice pioneered nonvolatile, reprogrammable logic with its UltraMOS® E²CMOS® technology. This technology, combined with the Lattice GAL® architectures, has established Lattice products as the industry-standard in low-density programmable logic. Lattice's ispLSI® and pLSI® families of high-density PLDs combine leadership performance and density with in-system programmability to establish the high-density programmable logic standard of the 1990s.

#### **What This Manual Contains**

This manual provides a comprehensive guide to using Lattice's In-System Programmable (ISPTM) devices and design tools. Compiled from information gathered from Lattice's customers and applications engineers, this manual demonstrates how easy it is to designin and go to full production with Lattice ISP silicon and software solutions. This manual not only describes the theory behind ISP, but also shows the practical, "how-to" implementation of ISP. By combining this manual with the latest Lattice Data Book and Handbook, the reader will have a comprehensive reference library to efficiently design and implement ISP solutions.

#### **Additional Information**

For information on product availability and pricing, please contact your Lattice Sales Representative or Distributor. A listing of all Lattice Sales Offices, Sales Representatives, and Distributors is included at the end of this manual.

For immediate help with technical questions or access to selected applications described inside, please call:

Applications Hotline

ispGAL®, ispGDS™, and GAL Products: Tel. 1-800-FASTGAL (327-8425)

FAX (503) 681-3037

ispLSI and pLSI Products: Tel. 1-800-LATTICE (528-8423)

FAX (408) 944-8450

Electronic Bulletin Board

ispGAL, ispGDS, and GAL Products: (503) 693-0215 ispLSI and pLSI Products: (408) 980-9814

# Table of Contents

| Section 1: ISP | Overview                                                  |        |

|----------------|-----------------------------------------------------------|--------|

|                | ISP Overview                                              | 1-1    |

|                |                                                           |        |

| Section 2: The | e Basics of ISP                                           |        |

|                | The Basics of ISP                                         | 2-1    |

|                | Hardware Basics                                           | 2-3    |

|                | Software Basics                                           | 2-37   |

| Section 3: ISP | Programming Options                                       |        |

|                | User In-System Programming Options                        | . 3-1  |

|                | In-System Programming on a PC or Sun Workstation          | . 3-3  |

|                | In-System Programming from an Embedded Processor          | . 3-11 |

|                | ATE Programming of ISP Devices                            | . 3-25 |

|                | Third-Party Programmers                                   | 3-47   |

| Section 4: App | plication Notes and Article Reprints                      |        |

|                | Selecting the Best Device for In-System Programmability   | . 4-1  |

|                | In-System Programmable Logic in High Volume Manufacturing | . 4-7  |

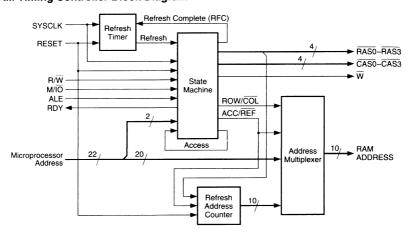

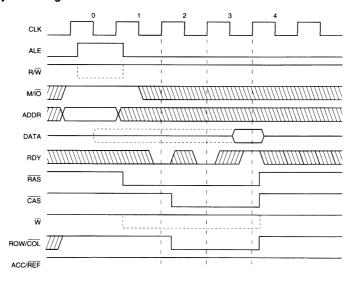

|                | ispLSI Configurable Memory Controller                     | . 4-15 |

|                | Lattice Bulletin Board Systems                            | 4-31   |

| Section 5: Ger | neral Information                                         |        |

|                | Lattice Sales Offices                                     | 5-1    |

| Index          |                                                           | .I-1   |

| Section 1: ISP | Overview                            |

|----------------|-------------------------------------|

|                | ISP Overview                        |

| Section 2: The | Basics of ISP                       |

| Section 3: ISP | Programming Options                 |

| Section 4: App | lication Notes and Article Reprints |

| Section 5: Gen | eral Information                    |

| Index          |                                     |

# ISP Overview

#### Introduction

ISP<sup>TM</sup> (In-System Programmability): The ability to reconfigure the logic and functionality of a device, board, or complete electronic system before, during, and after its manufacture and shipment to the end user.

ISP is the new standard in programmable device technology. ISP eliminates traditional PLD limitations and delivers benefits in board and system-level design, manufacturing, and programming. Since ISP hardware is as flexible and easy to modify as software, design upgrades are simple. Because ISP devices can be treated like any other device on the PCB, no special manufacturing flow is required to program ISP devices; standard 5-volt logic level programming signals are easily generated by a PC, Sun Workstation®, ATE (Automatic Test Equipment), or system embedded microprocessor. In pioneering ISP, Lattice has developed an integrated solution of silicon,

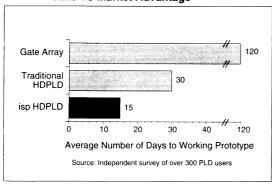

Figure 1. In-System Programmability: Time-To-Market Advantage

software and applications know-how that makes ISP a practical technology.

#### Q: What's Driving ISP Momentum?

#### A: Time-To-Market

The drive for a shorter time-to-market has fueled explosive growth in the use of PLDs.

Based on user responses, ISP provides an additional 50% reduction in time-to-market over traditional HDPLDs and a more than 85% reduction in time-to-market compared to gate array implementations (Figure 1).

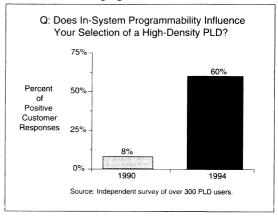

Another indicator of ISP's momentum is the percentage of designers who say that ISP capability will influence their selection of an HDPLD (Figure 2). Just four years ago, when asked, only 8% of system designers said that ISP would influence their HDPLD decision. Today, that percentage has leaped to 60%!

Figure 2. In-System Programmability:

An Emerging Standard

This overview presents the benefits of ISP and summarizes the ISP solutions available from Lattice. The outcome is convincing—ISP drives dramatic savings in design cycle time, manufacturing costs, and time-to-market.

#### ISP Design Benefits

ISP allows design, test, and manufacturing engineers to reconfigure system features while the devices remain soldered on the circuit board. This capability revolutionizes design prototyping, board-level debug, system manufacturing, and system upgrades.

#### The Superior Prototyping Solution

During most system design cycles, major board building blocks such as the microprocessor and RAM are selected first, well before system logic decisions are made. When using ispLSI devices, the designer can fully populate his prototype board with the major building blocks, interconnecting all functions with programmable logic and switch devices. Design changes, whether they require added or modified logic, can be made in minutes using Lattice's pDS or pDS+ software design tools. A 5-wire download cable from a PC or workstation to the prototype board downloads the new logic into the

#### ISP Overview

device(s). This ability to modify system functionality without changing components or printed circuit board (PCB) layout is only the first of many advantages afforded by Lattice's ISP technology.

#### **Internal Test**

Once the ISP logic has been stabilized, the designer may use the ISP devices to debug other portions of the board. For example, a circuit board frequently operates in a system where it is supplied with stimulus from other boards. The designer can use in-system programmability to debug system-level operation more quickly by reconfiguring the ISP devices to force or redirect signals (e.g. clocks or control signals) into various portions of the board design. This ability to thoroughly check board designs saves precious time during system-level debug and translates directly into a competitive time-to-market advantage.

#### **Board Reconfiguration and Field Upgrades**

ISP devices provide an ideal way to reconfigure boards and/or upgrade product features in the field. With conventional logic technology, a system installed at a customer site is very expensive and difficult to upgrade to the latest hardware revision, to fix hardware bugs, or to enable hardware options. With ISP devices, however, if a subsequent reconfiguration, upgrade or repair is required, a simple upgrade disk can be used, either in the field or the factory, to reconfigure the logic (e.g. to modify memory refresh or control logic or to operate with a faster microprocessor). Updates via modem, serial link, or a special ISP programming interface are possible depending on the system environment or needs.

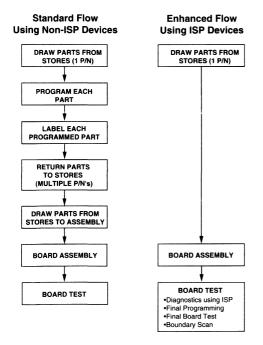

#### **ISP Manufacturing Benefits**

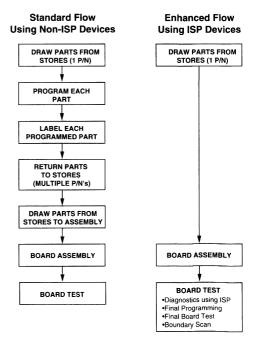

ISP is not only revolutionizing the world of logic design but is also dramatically transforming the world of manufacturing. The ISP devices support multi-function hardware designs that reduce system part count and cost. ISP also supports reconfigurability for test which enhances board-level testability and, ultimately, system reliability. Finally, ISP allows the "standard PLD manufacturing flow" to be simplified (Figure 3), reducing cost and enhancing system quality.

#### **Multi-Function Hardware**

ISP can be used to exploit the concept of multi-function hardware: a single hardware design able to implement a variety of system-level functions via in-system programming. Multi-function hardware allows manufacturers to reduce the number of unique board designs used in a system, further simplifying the manufacturing flow.

Multi-function hardware dramatically lowers system-level costs by reducing the component count on the boards as well as reducing the number of different boards required to implement various system-level options.

A dual-processor board, intended to interface with several bus interface standards, illustrates these benefits. The traditional solution calls for dedicated logic for each of the bus interface standards, requiring either a unique board dedicated for each standard or a single board with additional logic. ISP devices allow the design of a single generic bus interface, which can be configured in-system to interface with each of the bus standards, saving components, and cost.

#### **Reconfigurability for Test**

The ISP approach facilitates board-level testing and increases system fault coverage without sacrificing board resources or real estate. A diagnostic test pattern can be temporarily programmed into the ISP devices to exhaustively exercise board-level functions. Additionally, with ispGDS, programmable signal routing can be exploited in the test environment to perform enhanced board-level

Figure 3. ISP Manufacturing Flow vs. Standard Manufacturing Flow

test. For example, certain ispLSI devices may be configured by the tester to force test sequences into other portions of the board logic. The tester then monitors the response of this action and determines if the board passes or fails. This ability to detect board-level failures early in the manufacturing cycle reduces overall system cost. Once these detailed diagnostics are complete, the ISP devices can be reprogrammed to their normal logic configurations for final functional testing.

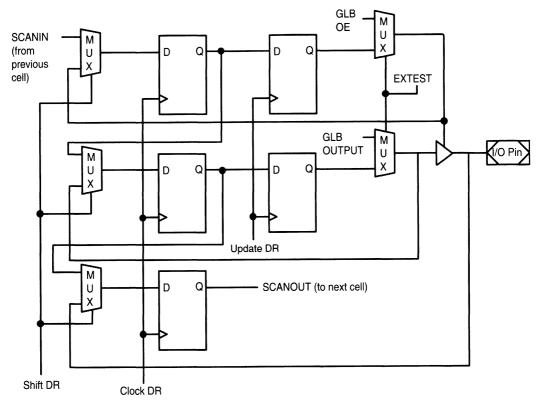

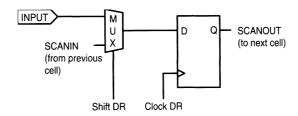

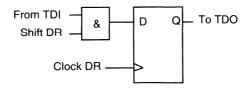

#### **Boundary Scan**

Complementing the ISP approach to board-level testing, IEEE Standard 1149.1 Boundary Scan technology (available with the 3000 series) enhances overall system quality. As component densities on the system boards increase, along with greater chip density and I/O, the ability to access and test critical nodes is impaired. With Boundary Scan Test, a serial interface through the test access port (TAP) simplifies field diagnostics and testing while costs are reduced. And because the same Boundary Scan serial path and control pins are used for implementing ISP programming, overall manufacturing costs are reduced as well.

### Simplified Manufacturing Flow / No Bent Leads

At present, there are no automatic handlers capable of handling the programming of high lead-count, high-density Quad Flat Pack PLDs. As a result, all non-ISP high lead-count devices must be programmed by hand using a standard logic programmer.

It is a difficult task to insert a high lead-count, small leadpitch device into a programming socket adapter, program, label (or mark) and reinventory the device without bending the delicate package leads. These bent leads can result in poor coplanarity and bad solder connections, increasing the amount of board and system-level troubleshooting required.

With the ISP devices, the parts go directly from the receiving dock to the manufacturing floor for placement on the PCB, entirely eliminating the stand-alone programming and mark operations and avoiding bent leads associated with misalignment of the device in the programmer socket. Unprogrammed ISP devices can be loaded into auto-insertion equipment and then placed directly onto the PCB without sockets or regard for the specific logic configurations. Individual device configurations can be downloaded from Automatic Test Equipment, PC, or workstation platforms at final board test. Programming of high-density PLDs containing thousands of gates takes only seconds.

#### **System Upgrades and Repair**

Lasting benefits from the use of ISP can be realized even after systems are shipped. In-system reprogramming can reduce field maintenance costs through enhanced field diagnostic capability, less costly product feature upgrades, and simpler maintenance procedures. Training, documentation, and on-going support can also be simplified by using the ISP approach to build in maintainability.

#### ISP Applications

Lattice's breadth of ISP device options, together with their leading-edge performance and features, have resulted in the design-in of ISP devices into a wide range of electronic systems. These applications include:

- · Multimedia Video Editing

- Electronic Test Equipment

- Network Routers and Bridges

- Cellular Telephone Base Stations

- · Telephone Switching Systems

- · Hardware Accelerators

- · Memory Subsystems

- · Multi-Standard Video Frame Grabber

- · Data Acquisition

- Image Processing

Why have designers embraced the ISP concept? For many, the manufacturing cost benefits, faster logic design and prototyping, and ability to reliably program high-pin count devices have been the most obvious benefits of employing ISP. However, in addition, ISP's ability to reconfigure systems immediately prior to and after shipment has begun to open up new possibilities.

For example, a very common but practical application for ISP comes from a company manufacturing traffic signal controllers. These controllers support priority "green lights" for emergency vehicles and buses through strobe light sensors that detect coded strobe sequences from the vehicles. The authorized sequences vary from city to city. ISP allows the sequence detector to be reprogrammed easily at the time the signal controller is shipped to a particular area or after it is installed. The alternative of custom-coded, traditional PLDs would result in significant additional effort and expense to customize the hardware of each system.

#### E2CMOS Technology

Lattice was the pioneer in electrically erasable CMOS ( $E^2$ CMOS) technology with the invention of the GAL device. With over 200 million devices shipped to customers, Lattice has the most CMOS PLD manufacturing experience in the industry. Merging  $E^2$ CMOS technology with ISP, Lattice conceived the in-system programmable, electrically erasable CMOS process. All ispLSI, ispGAL, and ispGDS devices are manufactured using Lattice's proprietary high-speed UltraMOS  $E^2$ CMOS technology. Lattice is unique among "fab-less" companies in that it performs its own process technology development. UltraMOS technology successfully combines the best features of CMOS and NMOS process technology to yield PLDs with the following key features:

- · Industry Leading Performance

- · High Logic Densities

- Low Power Consumption

- · Fast Erase and Reprogram Times (Seconds)

- 100% Full Parametric Testability

- 100% Programming and Functional Yields

Lattice's experience in E<sup>2</sup>CMOS manufacturing allows it to specify the best ISP parameters in the industry, including ISP programming over the full Commercial temperature range (0° to 70° C), a minimum of 1000 program / erase cycles for ispLSI devices (10,000 for ispGAL and ispGDS devices), and 20 year guaranteed program retention.

**Table 1. ISP Solutions from Lattice**

|                         | The Premier<br>High-Density PLD<br>1K, 2K, and 3K Families                                                          | World's First<br>In-System<br>Programmable 22V10 | In-System<br>Programmable<br>Switch Matrix |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|

| Density (PLD Gates)     | 1-14K Gates                                                                                                         | 500 Gates                                        | 7x7-11x11 Matrix                           |

| Speed: fmax (MHz)       | 135                                                                                                                 | 111                                              | 50                                         |

| Speed: <b>t</b> pd (ns) | 7.5                                                                                                                 | 7.5                                              | 7.5                                        |

| Macrocells              | 32-320                                                                                                              | 10                                               | N/A                                        |

| Registers               | 32-480                                                                                                              | 10                                               | N/A                                        |

| Inputs + I/Os           | 34-160                                                                                                              | 22                                               | 14-22                                      |

| Packages                | 44-, 68-, 84-Pin PLCC<br>44-, 100-, 176-Pin TQFP<br>120-, 128-Pin PQFP<br>160-, 208-Pin MQUAD<br>167-, 207-Pin CPGA | 28-Pin PLCC                                      | 20-, 28-Pin PLCC<br>20-, 24-, 28-Pin PDIP  |

Unlike SRAM-based programmable devices, the non-volatility of E<sup>2</sup>CMOS means there is never a need to reprogram ISP devices after a power-down and power-up sequence. In addition, there is no need for a separate memory component to store the logic program. A "security cell" feature is also available, allowing the device to be programmed, verified, and then secured. After the device has been secured, the binary pattern cannot be read from the device. However, even a secured device can be identified via the User Electronic Signature (UES). This field is reserved for the user to record product data such as code revisions and device functions.

#### ISP Solutions from Lattice

Lattice offers five families of In-System Programmable devices (Table 1).

# The ispLSI® Families of High-Density Programmable Logic from Lattice

The ispLSI families merge ISP technology with Lattice's high-performance, high-density pLSI® (programmable Large Scale Integration) architecture. The ispLSI devices are the first in-system programmable logic devices to combine the performance and ease of use of PLDs with the density and flexibility of FPGAs. Their powerful architecture can implement a wide range of logic functions including registers, counters, multiplexers, decoders, and complex state machines. With 135MHz system speed and logic densities ranging from 1,000 to 14,000 gates, they're the most powerful programmable logic components available today.

# The ispGAL® Family of Low-Density Programmable Logic from Lattice

The ispGAL family brings ISP technology to Lattice's industry standard GAL® (Generic Array Logic) family of Low-Density PLDs. The ispGAL22V10 combines the full functionality of the popular GAL22V10 architecture together with ISP technology, while maintaining the GAL22V10 standard 28-pin PLCC package and footprint.

At 7.5ns Tpd and 111MHz system speed, the ispGAL22V10 is ideally suited for high-speed, small- to medium-scale logic functions typically found at the heart of today's microprocessor based systems.

### The ispGDS™ Family of Programmable Digital Switches from Lattice

The ispGDS (in-system programmable Generic Digital Switch) family represents the expansion of ISP technology beyond system logic to system interconnect. This merger of ISP and a switch matrix architecture provides the ability to quickly implement and change p.c. board connections without changing mechanical switches or other system hardware. These high-performance, low-

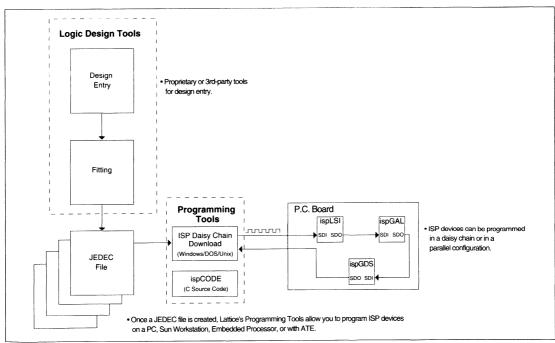

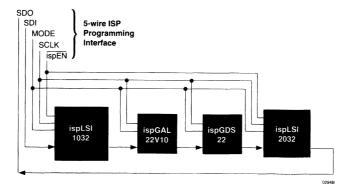

Figure 4. ISP Design and Implementation Flow

power, programmable digital switch devices are offered in a variety of matrix sizes and packages adding system flexibility to users.

The ispGDS family is an ideal solution for easy, endsystem feature configuration. With its 7.5ns performance, the ispGDS family also supports high-performance signal routing applications. The result is system hardware that can be reconfigured under software control without manual intervention.

#### ISP Implementation

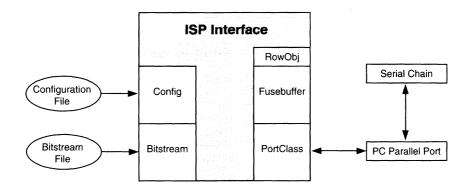

#### **ISP** Interface

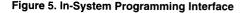

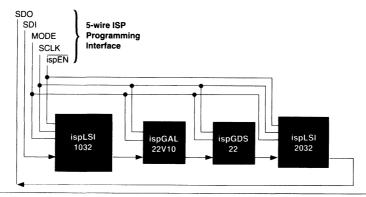

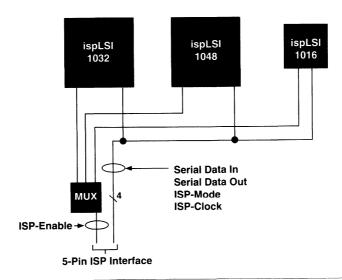

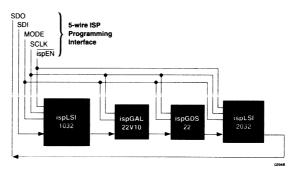

Programming and reprogramming ISP devices is simple and straightforward (Figure 4), requiring only a 5-volt power supply and a simple 4- or 5-wire serial interface depending on which ISP device is used. In-system programming operations such as PROGRAM, VERIFY, and ERASE are performed by passing commands and data to the ISP devices over the serial in-system programming interface (Figure 5). The basic programming signals consist of Serial Data In (SDI), MODE select (MODE), Serial Data Out (SDO) and Serial Clock (SCLK). In addition, ispEN is used to enable or disable the other four programming control signals on ispLSI devices, allowing these four pins to also function as dedicated inputs during normal operation.

#### ISP Overview

#### **Device Programming Configurations**

Single or multiple In-System Programmable (ISP) devices can be programmed in several configurations. Each ISP device can be programmed individually, through an independent ISP interface, or multiple devices can share a parallel multiplexed or serial daisy chained interface. The serial daisy chain configuration, shown in Figure 5, is the most efficient and easiest to implement, as it utilizes a simple hardware interface and programming procedures.

#### Multiple Programming Platforms

Lattice's ISP devices can be easily programmed on a wide variety of platforms:

#### **PC and Workstation**

Today, every engineer has a PC or workstation. With ISP, they save time and money by designing <u>and</u> prototyping logic on a single platform. Designers can enter and simulate designs using popular third-party CAE tools, automatically place-and-route the logic using Lattice's pDS or pDS+ tools, and then download the programming files to ISP devices without leaving their seat. With ISP, device programming is easy; Lattice's ispDOWNLOAD cable connects to the PC parallel port, or to the workstation's serial port (via the isp Engineering Kit Model 200), to give quick, easy and inexpensive programming of one or more ISP devices.

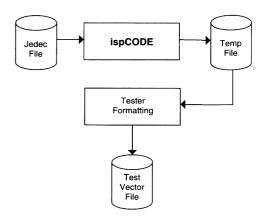

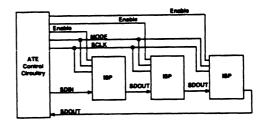

#### ATE

Lattice's ISP devices can also be programmed at final board test on an ATE, completely eliminating the need for a third-party device programmer for production. This streamlines the manufacturing flow and allows program-

mable devices for the first time to be treated like any other components on the board. To make the task easy, Lattice's ispCODE and tester programming utilities can be used to generate programming test vectors, or programming routines based on ispCODE can be written in the tester's high-level language.

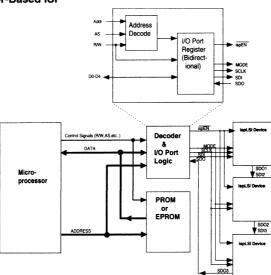

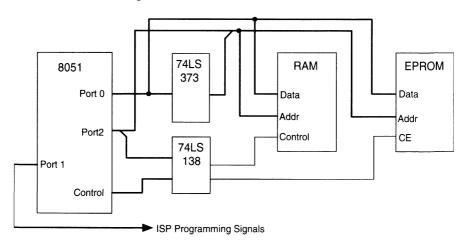

#### **Embedded Processor**

System Designers who want to be able to modify product features or upgrade their system hardware after the product has shipped to their customers will be interested in in-system programming using their product's own embedded processor. The product's embedded processor can be used to directly supply the ISP programming signals through a simple 4- or 5-bit port. Logic fuse maps and code can be stored in EPROM or other available system memory element. If the system has a modem or network link, remote download of new configurations from a central point is even possible. As result, systems no longer become obsolete as soon as they leave the factory, but can adapt and change to meet customers' growing needs for years to come.

#### **Third-Party Programmer**

Finally, ISP devices can be programmed by a number of popular third-party programmers. If a user already owns a third-party device programmer and is interested in the long-term benefits of ISP (like future field upgradability), but isn't ready to make the change yet, they can still program ISP devices like any other PLD on their device programmer. If they do need to change the device programming pattern at some future date, ISP will certainly make the process a lot easier: no device desoldering, no board swapping, no wasted effort.

#### **ISP Development Tools**

#### **Design Entry and Fitter Software**

To provide design support for in-system programmable devices, compiler support for ispGDS and ispGAL devices is available from numerous third-party compilers. ABEL, CUPL, LOG/iC, MINC, ORCAD PLD and others produce JEDEC files for these devices. Lattice also provides a compiler for the ispGDS family.

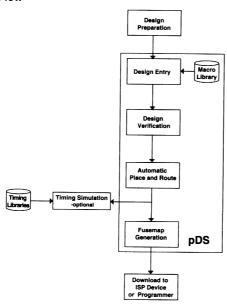

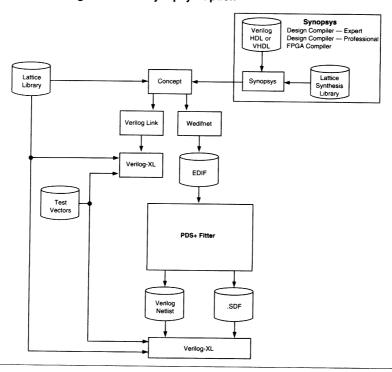

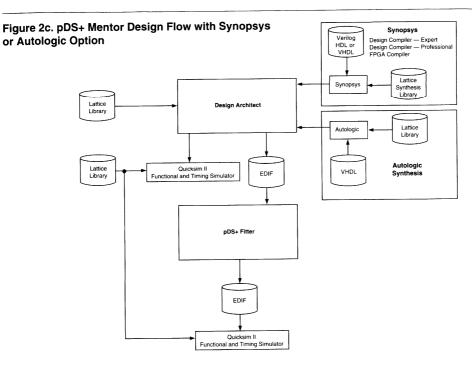

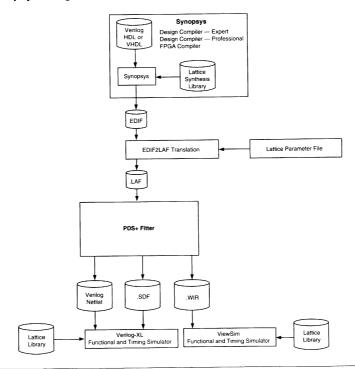

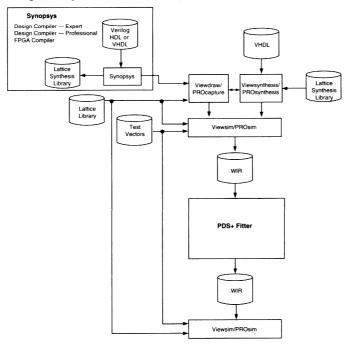

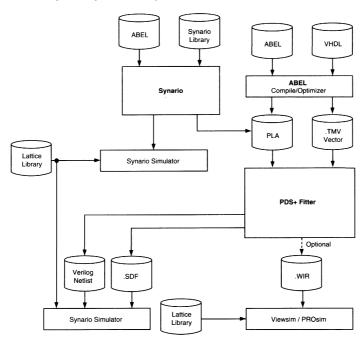

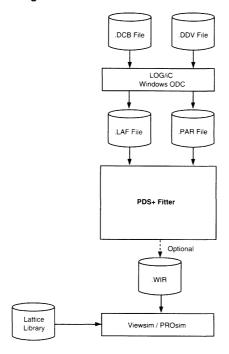

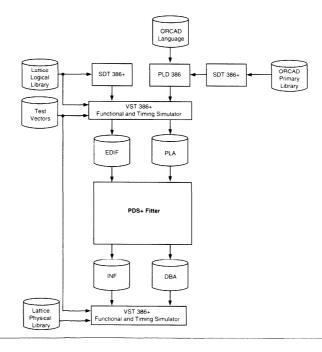

ispLSI designs can be quickly implemented using Lattice's low-cost pDS® development system or pDS+™ Fitter software that interfaces with third-party development software packages such as ABEL, Viewlogic, LOG/iC, Cadence, Synopsys, Mentor Graphics, Synario, and ORCAD (Figure 6), and produces standard JEDEC programming files.

#### ispStarter™ Kits

Lattice has also introduced products called ispStarter Kits that contain all the software, download cables, samples, and data sheets needed to implement ISP for the first time. These ispStarter Kits, available in pDS- and ABEL-compatible versions, allow system designers to try out ISP for themselves at a price of only \$99.

#### **Programming Tools**

Once the JEDEC file has been generated for a given design, the design information must be programmed into

the proper device. Lattice supports programming the ISP devices on a PC, workstation, embedded processor, ATE or third-party programmer with several programming tools.

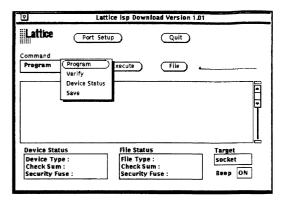

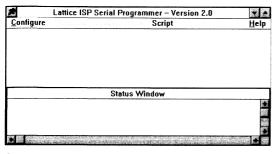

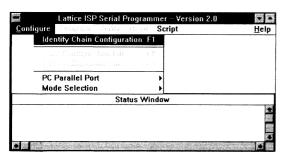

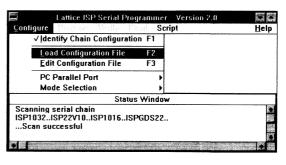

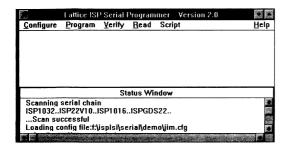

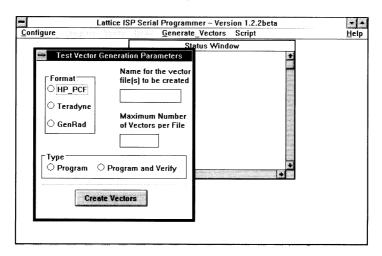

#### *ispCODE*

Lattice provides a library of programming routines written in ANSI-standard C++ language (called ispCODE<sup>™</sup>) which can be easily incorporated into a system or tester software to support programming of the ISP devices. These routines include such common operations as Program, Read, Verify, Erase, and Secure. After completion of the logic design and creation of a JEDEC file, in-system programming can be accomplished on customer-specific hardware: UNIX systems, PCs, testers, or embedded systems. The ispCODE software package supplies specific routines, with extensively commented source code, for incorporation into application programs. These routines provide flexible, easy-to-use program modules which support the programming of a single device or multiple devices on a board. Example programs are included to demonstrate the use of each routine. One of these programs, when compiled, produces a Windows application called ISP Serial Programmer, which not only programs, reads, and verifies ISP devices using the parallel port of a PC, but also supports ATE programmina.

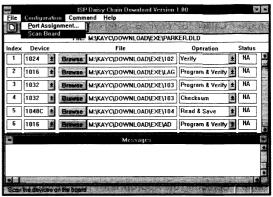

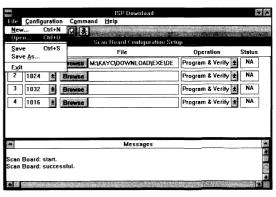

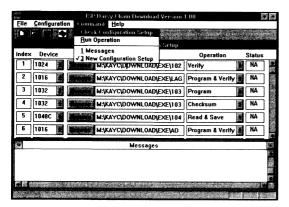

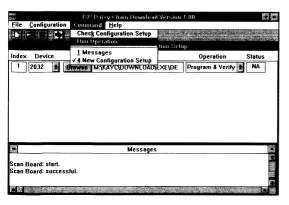

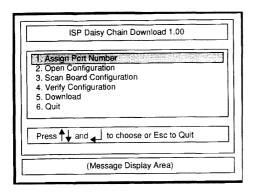

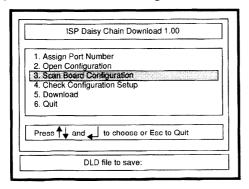

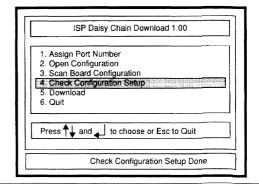

#### ISP Daisy Chain Download Software

Lattice also provides ISP Daisy Chain Download software, a Windows-based executable utility which supports

Figure 6. Development Tools Available from Lattice

#### ISP Overview

programming of all Lattice ISP devices in a serial daisy chain configuration in a PC environment.

#### isp Engineering Kits and Download Cable

Lattice's isp Engineering Kits for ispLSI devices function as device programmers in conjunction with a PC or workstation. Or, they can be used for direct download to an ispLSI device on your board. The isp Engineering Kits interface with either a PC or workstation and consist of a programming module, download cables and socket adapters which are used to program any of the Lattice ispLSI devices. The ispDOWNLOAD™ cable supports programming of any ISP device directly on the PCB.

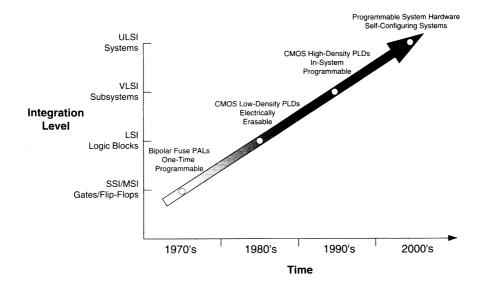

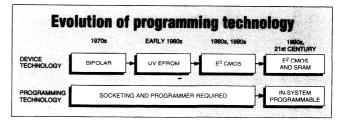

#### **Future of ISP**

In-system programmability is the logical evolution of programmable device technology. PLDs have evolved from the fuse-based, one-time programmable devices invented in the 70's, to the electrically erasable components of the 80's, and now the in-system programmable devices of the 90's. The time and expense benefits of employing ISP make its widespread use inevitable.

But what about the future applications that ISP opens up?

To begin with, system designers will need to adopt a new mindset to exploit hardware that can evolve after the product is shipped. No longer will a hardware design be "frozen" as it is today; features will change based on updates transmitted from a central site or the system microprocessor can reconfigure peripheral functions in response to application needs. The use of ISP will drive hardware designs to more generic configurations that are given their "personality" through in-system programmable logic and interconnect components. Entire boards will be able to reconfigure microprocessor, memory and peripheral functions for any application. Just as a PC can run CAE tools, financial spreadsheets, games and multimedia software depending on the need, ISP hardware will be able to solve a broad range of problems just by downloading a new personality.

Ultimately, ISP will make the term "hardware" an anachronism, and usher in the era of truly programmable systems.

#### **Programmable Technology Evolution**

#### Section 1: ISP Overview

| Section | 2.       | The | Danian | -4 100 |   |

|---------|----------|-----|--------|--------|---|

| Section | <i>-</i> | INE | Hagice | OT ISE | , |

| The Basics of ISP | 2 | -1  |

|-------------------|---|-----|

| Hardware Basics   | 2 | -3  |

| Software Basics   |   | -37 |

#### **Section 3: ISP Programming Options**

#### **Section 4: Application Notes and Article Reprints**

#### **Section 5: General Information**

#### Index

# The Basics of ISP

#### Introduction

This section describes the details of programming with Lattice's In-System Programmable (ISP™) devices. It is organized into three sections. The first section summarizes the ISP design flow. The next section describes ISP hardware interface basics, including discussions on both key issues required to get started with ISP quickly, as well as detailed ISP information for those interested in a thorough understanding of ISP at the device level. The final section focuses on ISP software, which summarizes all the development tools available to support easy implementation of the Lattice ISP solutions.

#### ISP Design Flow

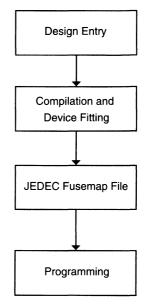

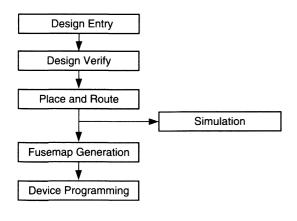

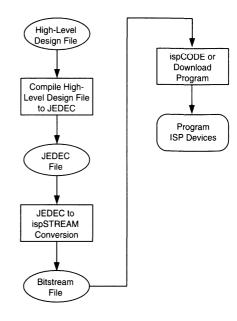

As with other Programmable Logic Devices (PLDs), the ISP design flow includes design entry using CAD software, compiling and fitting the design, generating a JEDEC standard fuse map file, and programming the device (Figure 1).

#### Creating a JEDEC Fuse map File

As part of any PLD design flow, the logic design must be entered through any combination of VHDL, schematic, Boolean equation, state machine, or truth table design entry. Lattice has various third-party and proprietary software packages which support these design methodologies. Each of these design packages will take a design and generate a standard JEDEC fuse map for programming. Up to this point in the logic design process, ISP devices share the same design flow as standard programmable logic devices.

#### **Programming**

Programming consists of converting the JEDEC fuse map file into a serial data format and shifting that serial data into the device. The ISP programming software automatically converts the JEDEC fuse map file into the serial data format which is programmed into the ISP device. However, a JEDEC file is made up of ASCII characters which use a relatively large amount of space, especially in environments in which storage space for the fuse map information is limited. In order to support these storage-critical environments, Lattice has defined an ispSTREAM™ data format which represents each fuse location with a single bit instead of an ASCII character. The ISP programming software also accepts this ispSTREAM format for programming.

Figure 1. ISP Design Flow

Once the fuse map is ready, it is just a matter of serially shifting the data into the device along with the appropriate addresses and commands. The basic ISP interface uses four wires to shift the JEDEC fuse map data into the device. An additional fifth wire is used by ispLSI devices, employing an active low ISP Enable (ispEN) signal as a mode control to put the device into programming or normal operation mode.

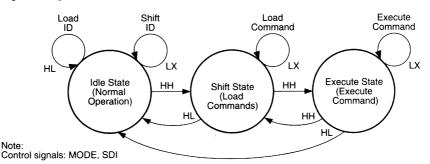

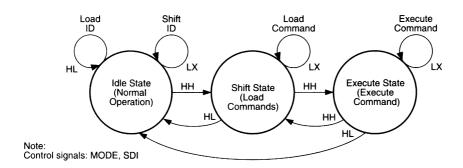

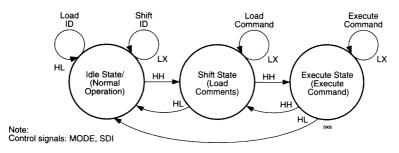

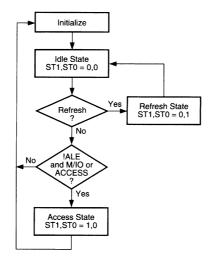

The MODE signal, along with SDI, controls the ISP device's internal state machine to step through the ISP programming process. The entire ISP programming process is controlled by a three-state state machine. The three states are Idle State, Shift State, and Execute State. Transitions between these states are controlled by the MODE and SDI inputs along with SCLK for synchronization. ISP commands such as Program, Bulk Erase, Verify, Data Shift, and Address Shift are executed through the device's instruction registers and ISP interface input pins.

#### The Basics of ISP

Traditionally, programmable logic devices have been programmed on PLD/PROM programmers which require that all programming signals and algorithms be generated by the programmer. The programmer also generates the external super voltage or high voltage required by non-ISP devices (typically 12-14 volts). This super voltage requirement is one of the main reasons dedicated programmers are used to program conventional PLDs.

However, with ISP devices, the ISP programming super voltage is generated within the device from the 5-volt power supply. This internal super voltage generation teamed with Lattice's unique serial ISP programming interface enables designers to program any ISP device using a simple four- or five-wire interface in which all the programming signals are driven by standard TTL logic levels (5 volts).

The details of device programming are transparent to the user if ISP programming software such as ISP Daisy Chain Download and ispCODE<sup>™</sup> C++ Source Code are used. These software tools drive the four or five ISP programming signals in accordance with the programming specifications and the state machine requirements. The ISP Daisy Chain Download software generates the ISP signals with proper timing through the use of the PC

parallel port. ispCODE can be ported to any hardware platform required and can be used to generate ISP programming signals using whatever hardware is available.

Lattice also supports the use of other programming interfaces such as Automatic Test Equipment (ATE). Specifically for testers, Lattice provides JEDEC file conversion routines to tester-acceptable formats. In addition, testers which accept high-level languages can be programmed using ispCODE C++ routines as a model for structuring test programs.

These and other topics are covered in the next two sections, "Hardware Basics" and "Software Basics."

In-System Programming (ISP) Interface

Programming Lattice's ispLSI, ispGAL, and ispGDS de-

#### Introduction

This section describes programming Lattice ISP devices from a hardware point of view. It is divided into two subsections. The first subsection "Getting Started Fast" is intended to give the reader enough ISP hardware information to easily implement Lattice's ISP solutions using the Lattice ISP tools. The second subsection "ISP Expert" gives more details on low-level, device-specific programming algorithms. Since these algorithms are transparently handled by Lattice's programming tools, the second subsection is intended for those readers who want a thorough understanding of the programming procedures, which would be required for any custom implementation of ISP.

| Subsection I "Getting Started Fast"   | Page |

|---------------------------------------|------|

| ISP Interface                         | 2-3  |

| ISP State Machine Operation           | 2-4  |

| ISP Device Programming Configurations | 2-5  |

| Hardware Considerations               | 2-7  |

| Hardware Programming Tools            | 2-9  |

| Programming Times                     | 2-10 |

| User Electronic Signature (UES)       | 2-11 |

|                                       |      |

| age |

|-----|

| 12  |

| 19  |

| 23  |

| 32  |

| 34  |

|     |

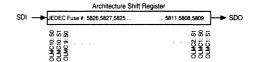

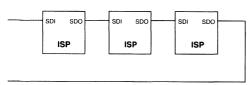

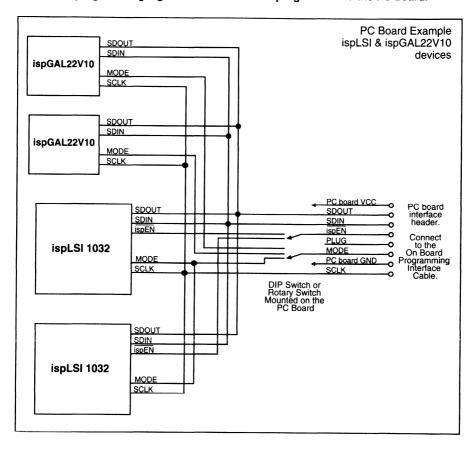

Figure 1. Multiple ISP Device Programming Interface

# vices is based on a simple serial ISP programming interface (Figure 1). The basic elements of the ISP programming interface are the mode control (MODE), serial data in (SDI), serial data out (SDO), and serial clock (SCLK) inputs, as well as a three-state programming control state machine integrated into each ISP device. Lattice's ISP devices utilize nonvolatile E<sup>2</sup>CMOS technology and require only five-volt, TTL-level programming signals from the ISP interface for in-system programming. The internal three-state state machine, which determines whether the device is in the normal operation state or in the programming states, is controlled by the four ISP programming pins. MODE and SDI furnish

control inputs to the state machine, SDI and SDO make up the programming data inputs and outputs to and from an internal shift register, and SCLK provides the clock. ispLSI devices use a fifth programming pin, ispEN, to multiplex the functions of the SDI, SDO, SCLK, and MODE pins between ISP functions during programming and user-defined logic functions during normal PLD

The internal state machine controls the sequence of programming operations such as identifying the ISP device, shifting in the appropriate data and commands, controlling the internal programming pulse widths to ensure proper programming voltage margins, and erasing the device. Programming consists of shifting the logic implementation stored in a JEDEC file into the device serially through the SDI pin along with the appropriate address and commands, programming the data into the E<sup>2</sup>CMOS logic elements, and shifting the data from the logic array out through the SDO pin for verification.

operation.

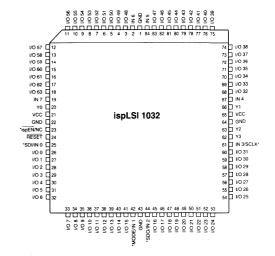

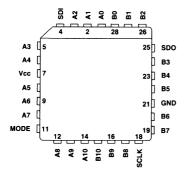

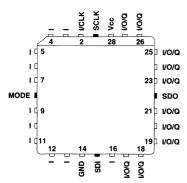

#### ISP Programming Pins

The programming pins used to program Lattice devices are each described in detail in this section. Figure 2 shows the ispLSI 1032 84-Pin PLCC device pinout.

The Serial Data In (SDI) pin performs two different functions. First, it acts as the data input to the serial shift register built inside each ISP device. Second, it functions as one of the two control pins for the programming state machine. Because of this dual role, the function of SDI is controlled by the MODE pin. When MODE is low, SDI becomes the serial input to the shift register, and when MODE is high, SDI becomes a control signal for the programming state machine. Internally, the SDI signal is multiplexed to various shift registers in the device. The different shift instructions of the state machine determine which of these shift registers receives input from SDI.

The MODE signal, combined with the SDI signal, controls the programming state machine, as described in the "ISP State Machine Operation" section which follows.

The Serial Clock (SCLK) pin provides the serial shift register with a clock. SCLK is used to clock the internal serial shift registers and clock the ISP state machine between states. State changes and shifting data in are performed on low-to-high transitions. When MODE is high, SCLK controls the programming state machine, and when MODE is low, SCLK acts as a shift register clock to shift data in or out or to start an operation. When shifting data out, the data is available and valid on SDO only after a subsequent high-to-low transition of SCLK.

The Serial Data Out (SDO) pin is connected to the output of the internal serial shift registers. As previously stated, the selection of which shift register to output is determined by the ISP state machine's shift instruction. When MODE is driven high, SDO connects directly to SDI, bypassing the device's shift registers.

Figure 3. Programming State Machine

Note:

Figure 2. ispLSI 1032 84-Pin PLCC Pinout Diagram

The ispEN pin, only utilized on the ispLSI devices, determines which mode the device is in, namely Edit Mode (ISP programming mode) or Normal Mode (normal device operation mode). When ispEN is driven low on an ispLSI device, the device I/O pins are put into a high impedance state (by internal active pull-up resistors equivalent to  $100K\Omega$ ) and the device enters Edit Mode.

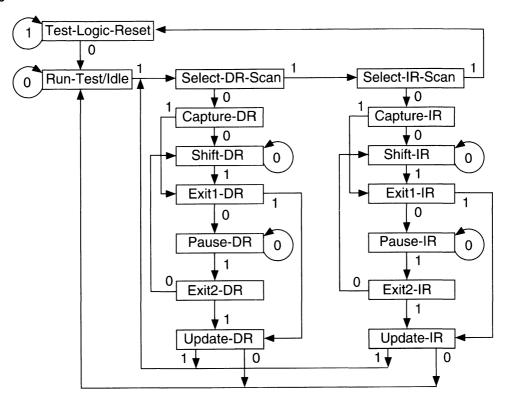

#### **ISP State Machine Operation**

The programming state machine controls which mode the device is in, and provides the means to read and write data to the device (Figure 3). Four ISP programming pins are used to load and unload data, and to control the state machine. The three states defined in the state machine diagram are the IDLE State, SHIFT State, and EXECUTE State. Instruction codes, which are shifted into the device in the SHIFT state, control which instruction is to be

executed in the EXECUTE state. In the SHIFT and EXECUTE states, all the I/O pins are 3-stated. To transition between states, MODE is held high, SDI is set to the appropriate level, and SCLK is clocked. The ispGAL22V10 and ispGDS devices, unlike ispLSI devices which employ an ispEN input pin, rely on the state machine to put the device I/O pins in a high impedance state. The IDLE state puts the ispGAL and ispGDS devices into Normal Mode, and the remaining two states put the devices into ISP programming mode, which places the device I/O pins in the high impedance state.

#### Idle/ID State

The Idle/ID state is the first state activated when the device enters the Edit Mode (ISP programming mode). The state machine is in the Idle/ID state when the device is idle, in the Edit Mode, or when the user needs to read the device identification (each ISP device type is assigned a unique identification code. See the "ISP Expert" section). The eight-bit device identification is loaded into the shift register by driving MODE high, SDI low, and clocking the ISP state machine with SCLK. Once the ID is loaded, it is read out serially by driving MODE low. Notice that when the device ID is read serially. SDI can either be high or low (called "don't care") and the state machine needs only seven clocks to read out eight bits of device ID. The default state for the control signals is MODE high and SDI low. State transition to the Command Shift State occurs when both MODE and SDI are high while the ISP state machine gets a clock transition. As with most shift registers, the Least Significant Bit (LSB) of the ID gets shifted out from SDO first.

#### **Command Shift State**

This state is strictly used for shifting instructions into the state machine. The entire instruction sets for the ispLSI, ispGDS, and ispGAL devices are listed in the "ISP Expert" section. When MODE is low and SDI is "don't care" in the Command Shift State, SCLK shifts the instruction into the state machine. Once the instruction is shifted into the state machine, the state machine must transition to the Execute State to execute the instruction. Driving both MODE and SDI high and applying the clock transfers the state machine from the Command Shift State to the Execute State. If needed, the state machine can move from the Command Shift State to the Idle/ID State by driving MODE high and SDI low.

#### **Execute State**

In the Execute State, the state machine executes instructions that are loaded into the device in the Command Shift State. For some instructions, the state machine requires more than one clock to execute the command. An example of this multiple clock requirement is the address or data shift instruction. The number of clock pulses required for these instructions depends on the device shift register sizes. When executing instructions such as Program, Verify, or Bulk Erase, the necessary timing requirements must be followed to make sure that the commands are executed properly. For specific timing information refer to the appropriate data sheets.

To execute a command, MODE is driven low and SDI is "don't care." For multiple clock instructions, the control signals must remain in the same state throughout the duration of the execution. MODE high and SDI high will take the state machine back to the Command Shift State and MODE high and SDI low will take the state machine to the Idle/ID State.

#### **ISP Device Programming Configurations**

#### **Serial Daisy Chain**

#### Advantages

One of the main advantages of daisy chained ISP programming is the simplified hardware interface. The number of ISP devices that can be connected to the same serial interface is limited only by the signal drive capability of the ISP programming control logic. One serial daisy chain is capable of providing the necessary programming interface, minimizing the hardware overhead for in-system programming. Software controls generated from PCs, microcontrollers, and test equipment can program and reconfigure ISP devices during various board-level design, test, and manufacturing stages.

#### **Programming Configuration**

As shown previously in Figure 1, all the MODE, SCLK, and ispEN (if using ispLSI devices) pins of the ISP devices are connected to the ISP interface, and the first device's SDO is connected to the second device's SDI, and each following SDO to the SDI of the next ISP device. This configuration allows a large string of ISP devices to be programmed, in-system, in a serial daisy chain.

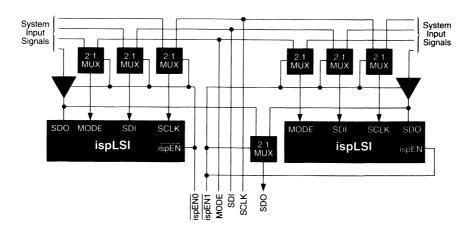

#### **Parallel**

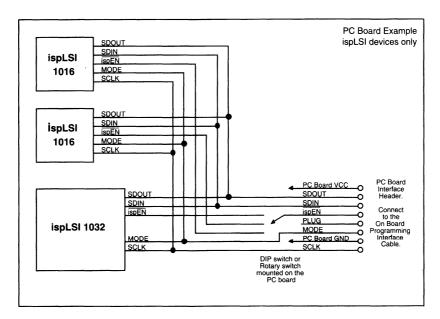

For low-density ISP devices daisy chain programming is the most common configuration, but for high-density devices, with multiplexed programming and logic pins and the ispEN feature, other programming configurations are also common. ISP devices can be programmed in one of two parallel configurations. The first parallel configuration, called Dedicated ISP Pins, dedicates all ISP programming pins to programming. The second parallel configuration, called Parallel Multiplex below, is mainly used for ispLSI devices. In this configuration, the functions of the ISP programming pins can be multiplexed between acting as programming pins and acting as inputs for normal logic functions.

#### **Dedicated ISP Pins**

Figure 4 illustrates one configuration for programming multiple ISP devices, where the ISP programming pins (MODE, SDI, SDO, and SCLK) are dedicated to programming functions. Although this scheme precludes the use of the ISP programming control signal pins as separate dedicated inputs for system logic functions on ispLSI devices, it is the easiest to implement. Each of the four programming control signal pins in each ISP device is connected (i.e. SDI of the ispLSI 1032 is connected to SDI of the ispLSI 1048 and SDI of the ispLSI 1016; MODE of the ispLSI 1032 is connected to MODE of the ispLSI 1048 and MODE of the ispLSI 1016; etc.). With this scheme, the ispEN signal for each ispLSI device is enabled (ispEN low) separately, and one device is placed in Edit (ISP programming) Mode at a time. With one

device in Edit Mode, the other devices will be in Normal Mode and can continue to perform normal system logic functions. ispEN is the only programming interface signal that cannot be used for general logic functions.

#### Parallel Multiplex

Figure 5 illustrates a multiplexing scheme which allows the user to control the ISP programming through multiple independent ispEN signals for the ispLSI devices. The multiple ispEN signals not only control the ispEN inputs of the ispLSI devices, but also act as the control signals for multiplexing the functional and ISP programming signals. This scheme differs from the previous one in that the ISP programming signals are not dedicated to programming. Instead, the ISP programming signals MODE, SDI and SCLK function as inputs for both normal functional mode and the ISP programming mode. SDO, however, functions as an input in normal functional mode and as an output in ISP programming mode. Figure 5 also shows the difference in controlling these different programming signals. Please note that when multiplexing the programming interface signals, the input driving the SDO pin must be 3-stated during programming to avoid signal contention. As previously stated, the ISP programming pins on the ispGAL and ispGDS devices are dedicated to ISP programming, so this configuration is not utilized often for the ispGAL and ispGDS devices. The concept can be modified to multiplex the MODE pin instead of the ispEN pin and becomes useful in some ispGAL and ispGDS applications.

Figure 4. Dedicated ISP Pins Configuration

Figure 5. Parallel Multiplex Configuration

#### **Hardware Considerations**

Lattice's In-System Programming (ISP) technology makes the use of Programmable Logic incredibly simple. Using ISP, multiple devices can be programmed using a single serial daisy chain programming loop. However, as with any high performance semiconductor component, systems must be designed to insure good signal integrity without signal conflicts between components. By doing so, reliable operation can be obtained over a wide range of operating conditions. This section discusses some basic programming hardware issues which should be considered when implementing a system using Lattice ISP.

All ISP programming specifications such as the programming cycle and data retention are guaranteed when programming ISP devices over the commercial temperature range (0 to 70° C). It is critical that the programming and bulk erase pulse width specifications are met by the programming platform to insure proper in-system programming. Lattice's ISP Daisy Chain Download and ispCODE software insures that these specifications are met when using a PC programming platform.

When using the ispDOWNLOAD cable in a daisy chained configuration, Lattice recommends using a maximum of eight ISP devices in a single chain. This is to insure proper programming signal integrity (pulse width, shape, etc.) at the ISP devices. The eight devices can be any combination of ispLSI, ispGAL, and ispGDS devices arranged in any order. The recommended number of devices is based on a typical system board environment with proper signal terminations and typical trace lengths. The actual number of devices that can be programmed in a serial chain may vary according to the system board environment. When using more than eight devices, additional buffering of the ISP programming signals is recommended. Alternatively, multiple programming loops can be employed which are electrically isolated from one another.

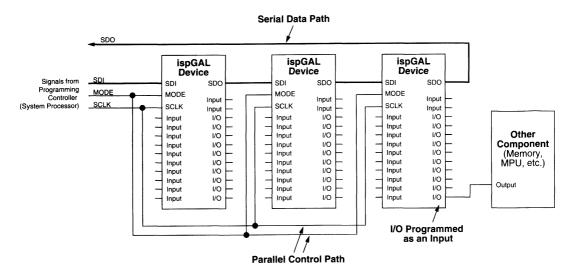

I/O pins on ISP devices may be defined as inputs once the devices are programmed. As a result, they typically will be driven by the outputs of other components once mounted on the board. Care must be taken to ensure that I/O pins are not enabled prematurely during programming. To do so when the device is partially programmed can cause contention with other signal drivers since I/O pins destined to be configured as inputs may not be 3-stated yet. This conflict can cause improper device programming and potential damage (Figure 6).

Figure 6. ISP Serial Daisy Chain

All ISP devices are shipped from Lattice with a fuse pattern that will put all I/O pins in the high impedance state prior to programming. The output 3-state is controlled by the ispEN signal on the ispLSI devices. For the ispGAL and ispGDS devices, the output 3-state is controlled by the programming state machine (Shift and Execute states 3-state the devices). When implementing custom ISP programming code, it is important for the ispGAL and ispGDS that the ISP state machine be kept within the Shift and Execute states until the completion of programming. This procedure keeps the partially programmed device or devices from conflicting with other components on the board.

ISP programming signal default states must be maintained during normal device operation. The  $\overline{ispEN}$  pin on the ispLSI devices has an internal pull-up to place the devices in normal functional mode when the pin is not driven externally. The ispGAL and ispGDS devices' MODE or SDI signals must be tied low through a 1.2K $\Omega$  pull-down resistor during normal functional mode (on-chip pull-downs are not provided). It is not acceptable to let these pins float during normal operation. In addition, it is recommended that the ispDOWNLOAD cable have its  $\overline{ispEN}$  signal tied to a decoupling capacitor (.01 $\mu F$ ) to ground on the system board.

#### **Hardware Programming Tools**

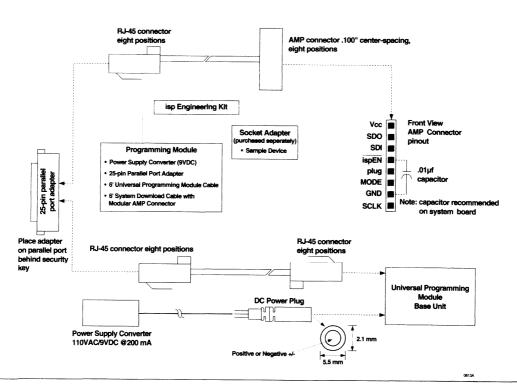

#### isp Engineering Kits

Lattice provides both a PC-based (Model 100) and a Sun Workstation-based (Model 200) isp Engineering Kit. The isp Engineering Kits function as stand-alone device programmers for prototyping.

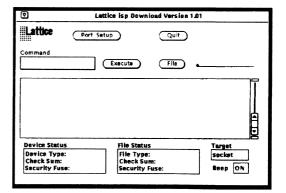

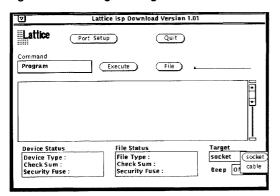

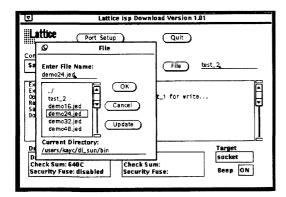

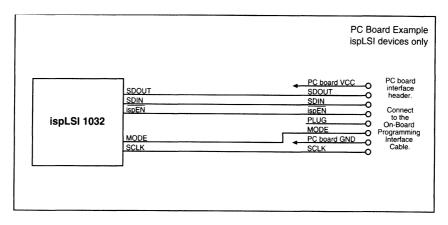

#### isp Engineering Kit Model 100

The isp Engineering Kit Model 100 provides designers with a quick and inexpensive means of evaluating and prototyping new designs using Lattice ispLSI devices. This kit is designed for engineering purposes only and is not intended for production use. The kit programs devices from the parallel printer port of a host PC using the Lattice pDS or pDS+ PC-based designs tools. By connecting a system cable (included) from the host PC to the isp Engineering Kit, or connecting from the host PC to the target device on the system board, a JEDEC file can be easily downloaded into the ispLSI device(s) (Figure 7).

#### Figure 7. ispEngineering Kit Model 100

#### isp Engineering Kit Model 200

The isp Engineering Kit Model 200 provides a prototyping solution for UNIX systems. This easy-to-use, inexpensive kit is designed for evaluating and prototyping new designs using Lattice ispLSI and pLSI devices. It is intended for engineering purposes only and is not intended for production use. The kit programs devices from the RS-232 serial port of a host workstation using the pDS+ workstation-based design tools by connecting a system download cable (included) from the host workstation to the isp Engineering Kit.

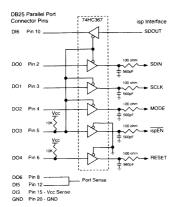

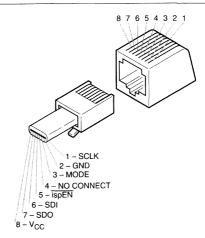

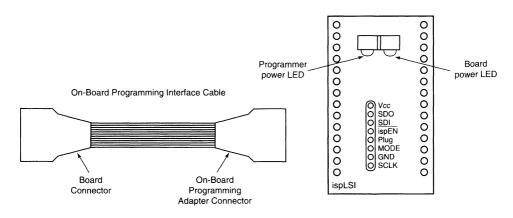

#### ispDOWNLOAD Cable

The ispDOWNLOAD Cable product is designed to facilitate in-system programming of all Lattice ISP devices on a printed circuit board directly from the parallel port of a PC. After completion of the logic design and creation of a JEDEC file by a logic compiler such as the pDS, pDS+Fitter or ispGDS Compiler software, Lattice's ISP Daisy Chain Download Software programs devices on the end-product p.c. board by generating programming signals directly from the parallel port of a PC which then pass through the ispDOWNLOAD Cable to the device. With this cable and a connector on the p.c. board, no additional components are required to program a device (Figure 8).

Figure 8. ispDOWNLOAD Cable

Note: The pin numbers in Figure 8 are for reference only. Do not use pin numbers as the socket pinout for board layout.

#### ispStarter Kits

The ispStarter Kits are designed to make Lattice's innovative in-system programmable device technology available in a single, complete package. The isp Starter Kits contain all the software, hardware, device samples, and information you need to begin designing with Lattice's ISP products.

The ispStarter Kits include pDS Starter or pDS+ ABEL logic development software for ispLSI 1016 and ispLSI 2032 devices, ispGDS compiler software, ispCODE, isp Daisy Chain Download Software, an ispLSI 2032-80LJ, an ispGAL22V10B-15LJ, an ispGDS14-7J, and an ispDOWNLOAD Cable.

#### **Programming Times**

The ISP programming times can be approximated by the number of rows that are required to program on a given device and the programming pulse width. Assuming that the overhead of shifting data and other miscellaneous functions are an order of magnitude smaller in time duration and therefore negligible, the total programming time ranges can be calculated as shown in Table 1.

**Table 1. Programming Times of ISP Devices**

| Device       | Total Programming Time in Seconds<br>( 40ms Programming Pulse) |

|--------------|----------------------------------------------------------------|

| ispGDS       | < 1                                                            |

| ispGAL22V10  | 1.84                                                           |

| ispLSI 1016  | 7.68                                                           |

| ispLSI 1024  | 8.16                                                           |

| ispLSI 1032  | 8.64                                                           |

| ispLSI 1048  | 9.60                                                           |

| ispLSI 1048C | 12.4                                                           |

| ispLSI 2032  | 8.16                                                           |

| ispLSI 3256  | 14.4                                                           |

#### User Electronic Signature (UES)

The Lattice ispGAL, ispGDS, and ispLSI families can ease problems associated with document control and device traceability, thanks to a feature called the User Electronic Signature (UES).

The UES is basically a user's "notepad" provided in electrically erasable (E²) cells on each ispGAL, ispGDS, and ispLSI device. The UES consists of an extra row that is appended to the programmable array and allocated for data storage. The physical size of the UES varies by device type. Table 2 indicates the various sizes of the UES.

In the course of system development and production, the proliferation of PLD architectures and patterns can be significant. To further complicate the record-keeping process, design changes often occur, especially in the early stages of product development. The task of maintaining which pattern goes into what device for which socket becomes exceedingly difficult. What's more, once a manufacturing flow has been set, it becomes important to "label" each PLD with pertinent manufacturing information, which is beneficial in the event of a customer problem or return.

**Table 2. UES Sizes**

| ISP Device   | UES Size (bits) |

|--------------|-----------------|

| ispGAL 22V10 | 64              |

| ispGDS       | 32              |

| ispLSI 1016  | 80              |

| ispLSI 1024  | 120             |

| ispLSI 1032  | 160             |

| ispLSI 1048  | 240             |

| ispLSI 1048C | 240             |

| ispLSI 2032  | 40              |

| ispLSI 3256  | 338             |

Lattice incorporated the UES to store such design and manufacturing data as the manufacturer's ID, programming date, programmer make, pattern code, checksum, PCB location, revision number, and/or product flow. This assists users with the complex chore of record maintenance and product flow control. In practice, the UES can be used for any of a number of ID functions.

Within the various bits available for UES data storage, users may find it helpful to define specific fields to make better use of the available storage. A field may use only one bit (or all bits), and can store a wide variety of information. The possibilities for these fields are endless, and their definition is completely up to the user.

Even with the device's security feature enabled, the UES can still be read. With a pattern code stored in the UES, the user can always identify which pattern has been used in a given device. As a second safety feature, when a device is erased and re-patterned, the UES row is automatically erased. This prevents any situation in which an old UES might be associated with a new pattern.

It is the user's responsibility to update the UES when reprogramming. It should be noted that UES information will be included in the checksum reading. Therefore, when the UES is modified the checksum will also change.

The UES may be accessed (read or write) through one of three methods. First, most third-party programmers support the UES option through the programmer's user interface, so programming or verifying the UES is as simple as programming or verifying any other array. Second, the UES may be embedded within the JEDEC file by selecting the proper fuse locations in the fuse map. Third, the UES can be written or read using Lattice's ispCODE software with routines provided in the ispCODE library. Further information on using ispCODE software to program the UES can be found in the Lattice Data Book.

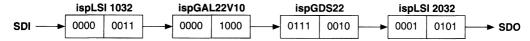

#### ispLSI Programming Details

The following sections describe the programmable state machine instruction set, timing parameters, device layout, and programming algorithms as they apply to ispLSI devices in general. Table 3 lists the eight-bit device ID's for all the ispLSI devices.

Table 4 lists the instructions that can be loaded into the state machine in the Command Shift State and then executed in the Execute State. Notice that the device identification is read during the Idle/ID State, and this operation does not require an instruction.

While it is possible to erase the individual arrays of the device, it is recommended that the entire device be erased (UBE) and programmed in one operation. This Bulk Erase operation should precede every programming cycle as an initialization.

When a device is secured by programming the security cell (PRGMSC), the on-chip verify and load circuitry is disabled. The device should be secured as the last procedure, after all the device verifications have been completed. The only way to erase the security cell is to perform a bulk erase (UBE) on the device.

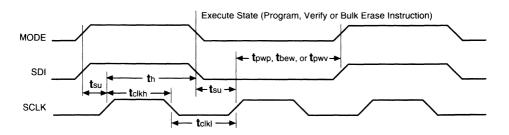

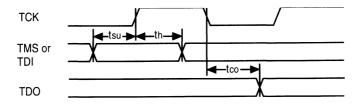

#### **Timing**

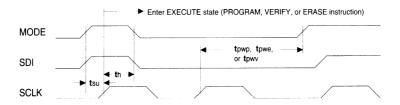

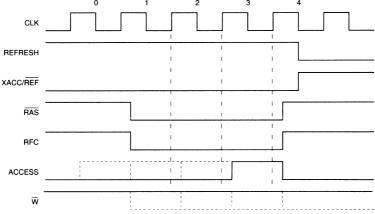

When programming ispLSI devices, there are several critical timing parameters that must be met to ensure proper programming. The two most critical parameters are the programming pulse width  $(t_{pwp})$  and the bulk erase pulse width  $(t_{bew})$ . These pulse widths determine the programming and erasing times of the  $\mathsf{E}^2$  cells. Figure 9 shows these critical program and erase timing specifications.

Table 3. ispLSI Device ID Codes

| Device       | MSB LSB  |

|--------------|----------|

| ispLSI 1016  | 0000001  |

| ispLSI 1024  | 00000010 |

| ispLSI 1032  | 00000011 |

| ispLSI 1048  | 00000100 |

| ispLSI 1048C | 00000101 |

| ispLSI 2032  | 00010101 |

| ispLSI 3256  | 00100010 |

In addition to the two programming and erasing specifications, the following timing specifications must be met.

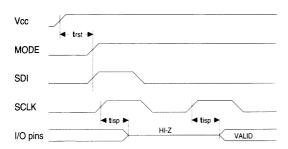

- tisp . Specifies the time it takes to get into the ISP mode after ispEN is activated. Or, the time it takes to come out from the ISP mode after ispEN becomes inactive.

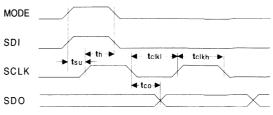

- Set up time of the control signals before SCLK. Or, the set up time of input signals against other control signals (if applicable).

- th Hold time of the control signal after SCLK. It also applies to the same input signals from the set up time.

- t<sub>clkl</sub> . Minimum clock pulse width, low.

- t<sub>clkh</sub> . Minimum clock pulse width, high.

- t<sub>pwv</sub> Verify or read pulse width. The minimum time requirement from the rising clock edge of a verify/load instruction execution to the next rising clock edge (Figure 9).

- $t_{rst}$  . Power on reset timing requirement.  $t_{rst}$  must elapse after power up before any operations are performed on the device.

All the programming timing parameters are summarized in the timing diagram (Figures 9 and 10).

Figure 9. ispLSI Program, Verify & Bulk Erase Timing

Figure 10. ispLSI Programming Timing Requirements

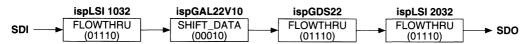

Table 4. ispLSI Programming State Machine Instruction Set

| •           | _         |                                                                                                                                                                                            |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction | Operation | Description                                                                                                                                                                                |

| 00000       | NOP       | No operation performed.                                                                                                                                                                    |

| 00001       | ADDSHFT   | Address Register Shift: Shifts address into the address shift register from SDIN.                                                                                                          |

| 00010       | DATASHFT  | Data Register Shift: Shifts data into or out of the data serial shift register.                                                                                                            |

| 00011       | UBE       | User Bulk Erase: Erase the entire device.                                                                                                                                                  |

| 00100       | GRPBE     | Global Routing Pool Bulk Erase: Bulk erases the GRP array only.                                                                                                                            |

| 00101       | GLBBE     | Generic Logic Block Bulk Erase: Bulk erases the GLB array only.                                                                                                                            |

| 00110       | ARCHBE    | Architecture Bulk Erase: Bulk erases the architecture array and I/O configuration only.                                                                                                    |

| 00111       | PRGMH     | Program High Order Bits: The data in the Data shift register is programmed into the addressed row's high order bits.                                                                       |

| 01000       | PRGML     | Program Low Order Bits: The data in the Data shift register is programmed into the addressed row's low order bits.                                                                         |

| 01001       | PRGMSC    | Program Security Cell: Programs the security cell of the device.                                                                                                                           |

| 01010       | VER/LDH   | Verify/Load High Order Bits: Load the data from the selected row's high order bits into the Data shift register for verification.                                                          |

| 01011       | VER/LDL   | Verify/Load Low Order Bits: Load the data from the selected row's low order bits into the Data shift register for verification.                                                            |

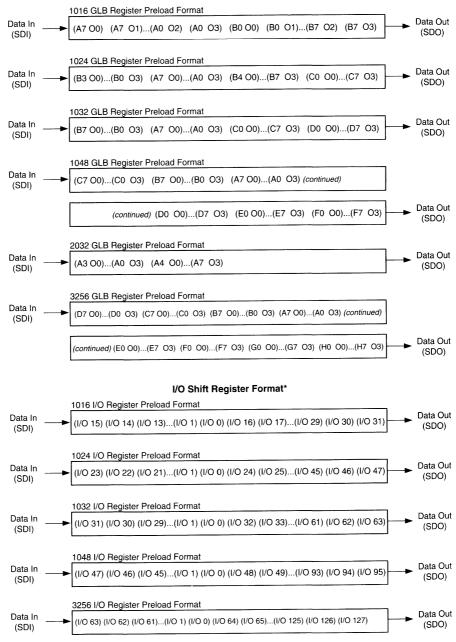

| 01100       | GLBPRLD   | Generic Logic Block Preload: Preloads the registers in the GLB with the data from SDIN. All registers in the GLB form a serial shift register. Refer to device layout section for details. |

| 01101       | IOPRLD    | I/O Preload: Preloads the I/O registers with the data from SDIN. All registers in the I/O cell form a serial shift register (the same order as GLB registers).                             |

| 01110       | FLOWTHRU  | Flow Through: Bypasses all the internal shift registers and SDOUT becomes the same as SDIN.                                                                                                |

| 10010       | VE/LDH    | Verify Erase/Load High Order Bits: Load the data from the selected row's high order bits into the Data shift register for erased verification.                                             |

| 10011       | VE/LDL    | Verify Erase/Load Low Order Bits: Load the data from the selected row's low order bits into the Data shift register for erased verification.                                               |

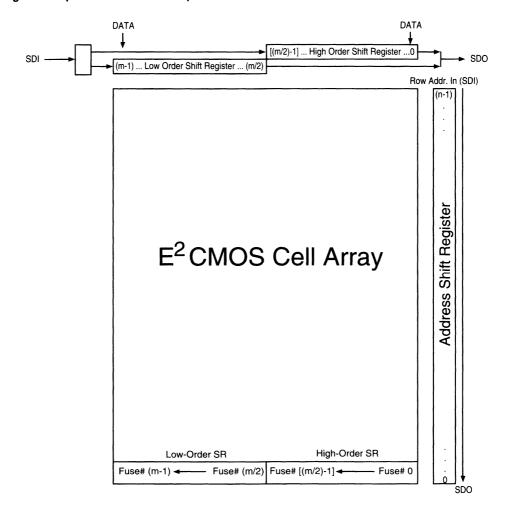

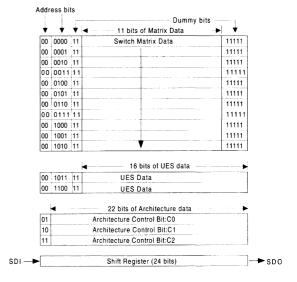

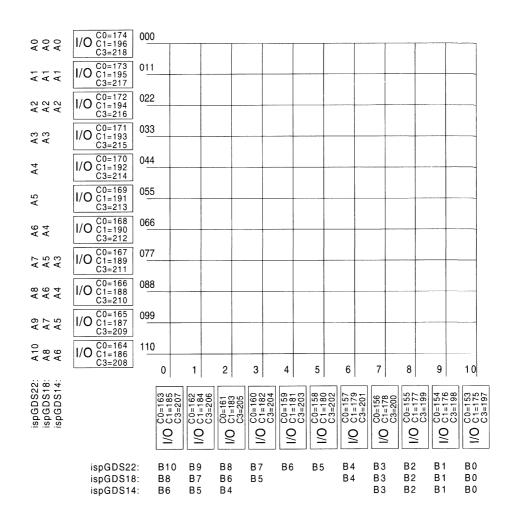

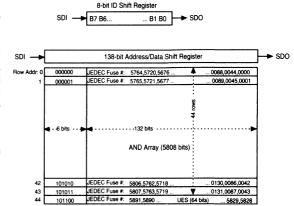

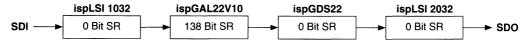

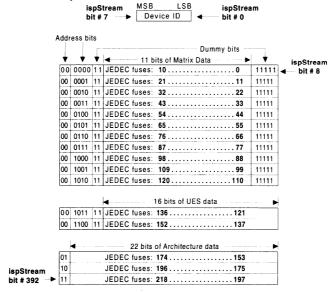

#### **Device Layout**

To translate the JEDEC format programming file into the serial data stream format for programming ispLSI devices, it is necessary to know the physical device layout and programming architecture. Two main factors determine how the translation must be implemented: the length of the address shift register and the length of the data shift register. The length of the address shift register indicates how many rows of data are to be programmed into the device. The length of the Data shift register indicates how many bits are to be programmed in each row. Both registers operate on a First In First Out (FIFO) basis, where the Least Significant Bit (LSB) of the data or address is shifted in first and the Most Significant Bit (MSB) of the data or address is shifted in last. For the Data shift register, the low order bits and the high order bits are separately shifted in.

Each ispLSI device has a predefined number of address rows and data bits needed to access its E<sup>2</sup>CMOS cells during programming. The data bits span the columns of the E<sup>2</sup> array. From this information, the number of programming cells (or fuses) are determined. Table 5 highlights the address and data shift register (SR) sizes for currently available ispLSI devices. The JEDEC file for these ispLSI devices will reflect the number of cells (fuses) seen in Table 5. The total number of cells becomes critical if the programming patterns are to be stored in an on-board memory storage of limited capacity such as EPROM or PROM.

The L-fields in the JEDEC programming file indicate the link or fuse numbers of the device. The first cell of the device is indicated by cell number L00000. L-fields of subsequent lines are optional. From this reference cell location, all other cell locations are determined by relative position. A zero (0) in the cell location indicates that the E² cell in that particular location is programmed (or has a logic connection intact). A one (1) in the cell location indicates that the cell is erased (equivalent to an open connection). The logic compiler software automatically generates this JEDEC standard programming file after the design has been fit into the device.

#### **Fuse Map to Device Conversion**

While the ispCODE software takes care of this detail, it is important to understand how the JEDEC fuse map is mapped onto the physical ispLSI device during programming. The physical layout of the fuse pattern begins with Address Row 0 and ends with the maximum Address Row N and is determined by the length of the Address SR as described in Table 5. Spanning the Address Rows are the outputs of the High-Order Data SR and Low-Order Data SR, as described in Table 6. Programming fuses on a given row are enabled by a "1" within the Address Shift Register for the appropriate row and the use of state machine instructions that selectively operate on the High-Order Data SR or the Low-Order Data SR. For example, the PRGMH instruction programs the High-Order data bits within the device for the selected Address Row and the PRGML instruction programs the Low-Order data bits (Table 4 lists the ISP state machine instructions). Referring to Figure 11, the starting cell (L00000) of the JEDEC fuse map shifts into the device at the physical location corresponding to Address Row 0, High-Order Data SR bit 0. The "n" and "m" in the figure refer to the Address SR length and the Data SR length, respectively, of the device (Table 5). A series of sequential shifts eventually results in the last cell location (Total # of Cells - 1) of the JEDEC fuse map shifting into Address Row (n-1), Low-Order Data SR bit (m-1) on the actual device.

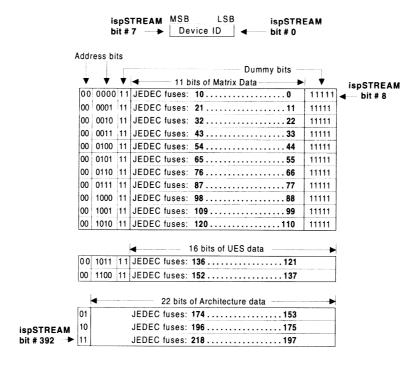

The ispCODE Software routines make use of a bit packed data format, called ispSTREAM™, to transfer data between the JEDEC fuse map and the physical device locations. The binary ispSTREAM format uses one bit to represent the state of each of the programmable cells, instead of the byte value used in an ASCII JEDEC file. Considering the additional characters present in a JE-DEC file, this adds up to a space savings of more than a factor of eight. In addition, the ispSTREAM does not require any parsing; the bits are simply read from the file and shifted into the device. As only 804 bytes are required to store the pattern for an ispGAL device, multiple patterns can be stored in a small amount of memory. The JEDEC fuse map can be translated into ispSTREAM format using the isp\_jedtoisp function and the ispSTREAM format can be translated into a JEDEC fuse map using the isp\_isptojed function.

Table 5. ispLSI Address and Data Shift Register and Total Cell Summary

|                        | ispLSI 1016 | ispLSI 1024 | ispLSI 1032 | ispLSI 1048/C | ispLSI 2032 | ispLSI 3256 |

|------------------------|-------------|-------------|-------------|---------------|-------------|-------------|

| Address SR Length      | 96          | 102         | 108         | 120/155       | 102         | 180         |

| Data SR Length/Address | 160         | 240         | 320         | 480/480       | 80          | 676         |

| Total Number of Cells  | 15,360      | 24,480      | 34,560      | 57,600/74,400 | 8,160       | 121,680     |

Table 6. Summary of ispLSI Data Shift Register Bits

| Data SR Bits           | ispLSI 1016 | ispLSI 1024 | ispLSI 1032 | ispLSI 1048/C | ispLSI 2032 | ispLSI 3256 |

|------------------------|-------------|-------------|-------------|---------------|-------------|-------------|

| High Order Data SR LSB | 0           | 0           | 0           | 0             | 0           | 0           |

| High Order Data SR MSB | 79          | 119         | 159         | 239           | 39          | 337         |

| Low Order Data SR LSB  | 80          | 120         | 160         | 240           | 40          | 338         |

| Low Order Data SR MSB  | 159         | 239         | 319         | 479           | 79          | 675         |

| Data SR Size (Bits)    | 160         | 240         | 320         | 480           | 80          | 676         |

Figure 11. ispLSI Device to Fuse Map Translation

### **Algorithms**

#### Command Stream

The first step in programming an ispLSI device is to determine the device type to be programmed. This is ascertained by reading the eight-bit ID of every device. By keeping SDI to a known level (either high or low), the ID shift can be terminated when a sequence of eight ones or eight zeros is read. From the device ID, the serial bit stream for programming can be arranged. A typical programming sequence is listed below:

- 1) ADDSHFT command shift

- 2) Execute ADDSHFT command

- 3) Shift address

- 4) DATASHFT command shift

- 5) Execute DATASHFT command

- 6) Shift high order data

- 7) PRGMH command shift

- 8) Execute PRGMH

- 9) DATASHFT command shift

- 10) Execute DATASHFT command

- 11) Shift low order data

- 12) PRGML command shift

- 13) Execute PRGML

- 14) Repeat from 1) until all rows are programmed

### Diagnostic Register Preload

This section explains how to preload all of the buried registers and I/O registers to a known state to test the logic function of a device. The process of loading the register reduces the time necessary to test a function that is deeply embedded in the logic of an ispLSI device.

To preload a device, the ISP state machine uses the same five pins as are used for programming (ispEN, SDI, MODE, SDO and SCLK). Two state machine commands preload all of the registers: GLBPRLD and IOPRLD. These commands enable two shift registers and allow data to be loaded into the device. The steps for loading data into the device are listed below:

- Enter the ISP programming mode by driving ispEN to Vil.

- 2. Load command GLBPRLD and execute command (wait one tclk).

- 3. Clock in the GLB preload data.

- 4. Load the command IOPRLD and execute the command (wait one tclk).